### Процессоры цифровой обработки сигналов

Процессоры цифровой обработки сигналов представляют собой класс специализированных микропроцессоров, предназначенных для решения задач **цифровой обработки сигналов** (ЦОС), к которым относятся обработка звуковых сигналов, обработка изображений, распознавание речи, распознавание образов, цифровая фильтрация, спектральный анализ и др.

Часто в литературе такие микропроцессоры называются **цифровыми сигнальными процессорами** (ЦСП), или DSP ( Digital Signal Processors ).

Первые процессоры этого класса появились в конце 1970-х годов. Требования практики, связанные с широким развитием мобильной беспроводной связи, стационарных систем широкополосной связи, использованием цифровой обработки сигналов в бытовой аудио- и видеотехнике и устройствах компьютерной периферии, с одной стороны и колоссальный прогресс электронной промышленности с другой привели к тому, что к настоящему времени производительность ЦСП возросла до сотен миллионов операций в секунду, а цена упала более чем на 90 % и даже для самых мощных процессоров составляет в настоящее время менее \$20.

Низкая потребляемая мощность (менее 1 Вт на максимальной частоте работы процессора) обеспечивает их широкое использование в различных встраиваемых устройствах от бытовой электроники до бортовых систем специального назначения.

#### Процессоры цифровой обработки сигналов

Цифровая обработка сигналов - это арифметическая обработка последовательности значений амплитуд сигнала, получаемых через равные промежутки времени. Главное, что отличает эту информацию, - она необязательно заносится в память и поэтому может оказаться недоступной в будущем. Следовательно, обрабатывать ее нужно в реальном масштабе времени (РМВ).

К основным особенностям цифровой обработки сигналов, которые во многом определяют архитектуру процессоров DSP, относятся:

- поточный характер обработки больших объемов данных в РМВ;

- обеспечение возможности интенсивного обмена с внешними устройствами.

Для эффективной реализации алгоритмов цифровой обработки сигналов необходима аппаратная поддержка базовых операций ЦОС. Поэтому рассмотрим вначале принципы цифровой обработки сигналов, оказывающие особое влияние на архитектуру ЦСП.

Любой аналоговый сигнал можно представить в виде характеристик -либо амплитудавремя, либо частота-амплитуда.

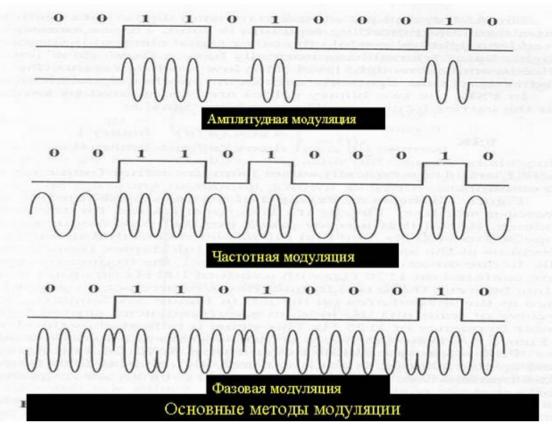

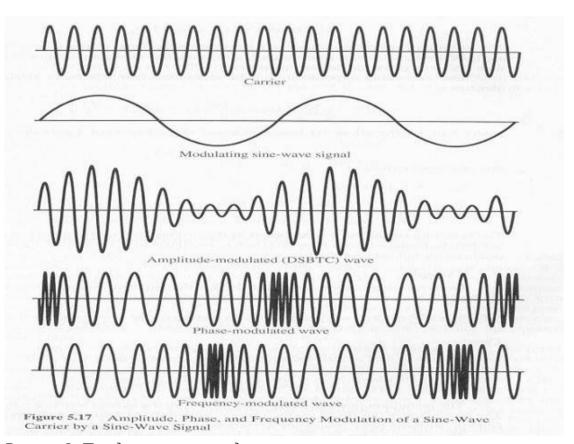

Рисунок 1: Передача цифровых данных в аналоговом сигнале

Рисунок 2: Передача аналоговых данных в аналоговом сигнале

Для перехода от одной формы представления к другой используется **преобразование Фурье**. Операции, выполняющие это преобразование, являются базовыми в **цифровой обработке сигналов**.

**Преобразование Фурье** представляет собой в общем случае работу с некоторой непрерывной функцией. С непрерывным преобразованием Фурье удобно работать в теории, но на практике мы обычно имеем дело с дискретными данными. Для обработки звуковых и видеосигналов в компьютере они сначала преобразуются в цифровую форму и представляются в виде некоторого набора отсчетов частот и амплитуд, производимых через определенные промежутки времени (период дискретизации). Поэтому здесь стоит говорить не об интегральном, а о **дискретном преобразовании Фурье** (ДПФ).

Пусть дана конечная последовательность чисел  $x_0, x_1, x_2, ..., x_{N-1}$  (в общем случае комплексных). Дискретное преобразование Фурье заключается в поиске другой последовательности  $X_0, X_1, X_2, ..., X_{N-1}$ , элементы которой вычисляются по формуле:

$$X_k = \sum_{n=0}^{N-1} x_n e^{\frac{-j2\Pi * kn}{N}}$$

Пусть дана конечная последовательность чисел  $X_0, X_1, X_2, ..., X_{N-1}$  (в общем случае комплексных). Обратное дискретное преобразование Фурье заключается в поиске другой последовательности  $x_0, x_1, x_2, ..., x_{N-1}$ , эле менты которой вычисляются по формуле:

$$x_n = \frac{1}{N} \sum_{k=0}^{N-1} X_k e^{-1}$$

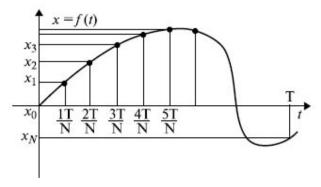

Рассмотрим теперь функцию x = f(t), представляющую собой некоторое звуковое или какое-либо иное колебание. Пусть это колебание описано графиком на временном интервале [0, T]

Для обработки этого сигнала в компьютере нужно выполнить его дискретизацию. С этой целью временной интервал делится на N-1 частей

Рисунок 3: Дискретизация сигнала

и сохраняются значения функции  $\mathbf{x}_0, \, \mathbf{x}_1, \, \mathbf{x}_2, \, ..., \, \mathbf{x}_{N-1}$  для N точек на границах интервалов.

В результате **прямого дискретного преобразования Фурье** могут быть получены N значений для  $X_k$ .

Если теперь применить **обратное дискретное преобразование Фурье**, то получится исходная последовательность  $\{x_n\}$ . Исходная последовательность состояла из действительных чисел, а последовательность  $\{X_k\}$  в общем случае комплексная.

Физический смысл **дискретного преобразования Фурье** состоит в том, чтобы представить некоторый дискретный сигнал в виде суммы гармоник. Параметры каждой гармоники вычисляются прямым преобразованием Фурье, а сумма гармоник - обратным.

Теперь, например, операция "фильтр нижних частот", которая "вырезает" из сигнала все частоты выше некоторой заданной, может просто обнулить коэффициенты, соответствующие частотам, которые необходимо удалить. Затем, после обработки, выполняется обратное преобразование.

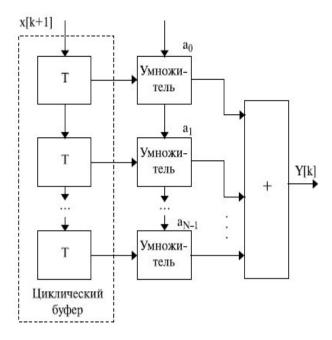

# Особенности цифровой обработки сигналов рассмотрим на примере алгоритма нерекурсивной фильтрации.

Структура устройства, реализующего данный алгоритм, показана на рисунке

Рисунок 4: Схема работы нерекурсивного фильтра

Обработка заключается в формировании выходного сигнала Y[k] по значениям N последних входных отсчетов x[k], которые поступают на вход устройства через определенный интервал времени Т. Принятые отсчеты сохраняются в ячейках циклического буфера. При приеме очередного отсчета содержимое всех ячеек буфера переписывается в соседнюю позицию, самый старый отсчет покидает буфер, а новый записывается в его младшую ячейку.

Аналитически алгоритм работы нерекурсивного фильтра записывается как:

$$Y[k] = \sum_{i=1}^{N-1} x[k-1]_{16.9}$$

где а<sub>і</sub> - коэффициенты, определяемые типом фильтра.

Отсчеты с выходов элементов буфера поступают на умножители, на вторые входы которых поступают коэффициенты  $a_i$ . Результаты произведений складываются и формируют отсчет выходного сигнала Y[k], после чего содержимое буфера сдвигается на 1 позицию и цикл работы фильтра повторяется.

Выходной сигнал Y[k] должен быть вычислен до поступления следующего входного сигнала, то есть за интервал Т. В этом заключается суть работы устройства в реальном масштабе времени.

Интервал времени Т задается частотой дискретизации, которая определяется областью применения фильтра.

При обработке звукового сигнала частоту дискретизации можно принять в 40 кГц.

В этом случае если необходимо реализовать цифровой нерекурсивный фильтр 50-го порядка, то за время в 1/40 кГц = 25 мкс должно быть выполнено 50 умножений и 50 накоплений результатов умножения. Для обработки видеосигнала интервал времени, за который должны быть выполнены эти действия, будет на несколько порядков меньше.

Если выполнять ДПФ входной последовательности напрямую, строго по исходной формуле, то потребуется много времени. Посчитав по определению ( N раз суммировать N слагаемых), получаем величину порядка  $N_2$ .

Тем не менее, можно обойтись существенно меньшим числом операций.

## Архитектура DSP

Однокристальные микроконтроллеры и даже универсальные микропроцессоры оказываются относительно медленными при выполнении операций, характерных для ЦОС. К тому же требования к качеству преобразования аналоговых сигналов постоянно возрастают. В сигнальных микропроцессорах такие операции поддерживаются на аппаратном уровне и выполняются, соответственно, достаточно быстро. Работа в реальном масштабе времени требует от процессора также поддержки на аппаратном уровне таких действий, как обработка прерываний, программных циклов.

Все это приводит к тому, что DSP-процессоры, архитектурно включая в себя многие черты как универсальных микропроцессоров, особенно с RISC-архитектурой, так и однокристальных микроконтроллеров, в то же время значительно отличаются от них. Универсальный микропроцессор помимо чисто вычислительных операций выполняет функцию объединяющего звена всей микропроцессорной системы, в частности компьютера.

Он должен управлять работой различных компонентов аппаратного обеспечения, таких как дисководы, графические дисплеи, сетевой интерфейс, с тем чтобы обеспечить их согласованную работу. Это приводит к достаточно сложной архитектуре, поскольку она должна поддерживать наряду с целочисленной арифметикой и операциями с плавающей запятой такие базовые функции, как защита памяти, мультипрограммирование, обработка векторной графики и т. п. В итоге типичный универсальный микропроцессор с СІЅС-, а зачастую и RISC-архитектурой имеет систему из несколько сотен команд, которые обеспечивают выполнение всех этих функций, и соответствующую аппаратную поддержку. Это ведет к необходимости иметь в составе такого МП десятки миллионов транзисторов.

В то же время **DSP-процессор** является узкоспециализированным устройством. Его единственная задача - быстро обрабатывать поток цифровых сигналов. Он состоит главным образом из высокоскоростных аппаратных схем, выполняющих арифметические функции и манипулирующих битами, оптимизированных таким образом, чтобы быстро обрабатывать большие объемы данных. В силу этого набор команд у DSP куда меньше, чем у универсального микропроцессора: их число обычно не превышает 80. Это значит, что для DSP требуется облегченный декодер команд и гораздо меньшее число исполнительных устройств. Кроме того, все исполнительные устройства в конечном итоге должны поддерживать высокопроизводительные арифметические операции. Таким образом,

типичный **DSP-процессор** состоит не более чем из нескольких сот тысяч (а не десятков миллионов, как в современных CISC-МП) транзисторов. В силу этого такие МП потребляют меньше энергии, что позволяет использовать их в продуктах, работающих от батарей. Крайне упрощается их производство, поэтому они находят себе применение в недорогих устройствах. Сочетание низкого энергопотребления и невысокой стоимости позволяет использовать их не только в высокой сфере телекоммуникаций, но и в сотовых телефонах и роботах-игрушках.

Отметим основные **особенности архитектуры процессоров цифровой обработки сигналов**:

- 1. Гарвардская архитектура, основу которой составляет физическое и логическое разделение памяти команд и памяти данных. Ключевые команды DSP-процессора являются многооперандными, и ускорение их работы требует одновременного чтения нескольких ячеек памяти. Соответственно на кристалле имеются раздельные шины адреса и данных (в некоторых типах процессоров несколько шин адреса и данных). Это позволяет совмещать во времени выборку операндов и исполнение команд. Использование модифицированной гарвардской архитектуры предполагает, что операнды могут храниться не только в памяти данных, но и в памяти команд вместе с программами. Например, в случае реализации цифровых фильтров коэффициенты могут храниться в памяти программ, а значения данных в памяти данных. Поэтому коэффициент и данные могут выбираться в одном машинном цикле. Для обеспечения выборки команды в том же машинном цикле используется либо кэш-память программ, либо двукратное обращение к памяти программ за время машинного цикла.

- 2. Для сокращения времени выполнения одной из основных операций цифровой обработки сигнала умножения применяется аппаратный умножитель. В процессорах общего назначения эта операция реализуется за несколько тактов сдвига и сложения и занимает много времени, а в **DSP-процессорах** благодаря специализированному умножителю нужен всего один цикл. Встроенная схема аппаратного умножения позволяет выполнить за 1 такт основную операцию ЦОС умножение с накоплением ( MultIPly-Accumulate MAC ) для 16- и/или 32-разрядных операндов.

- 3. Аппаратная поддержка циклических буферов. Например, для фильтра, представленного на рисунке 4 при каждом вычислении отсчета выходного сигнала используется новый отсчет входного сигнала, который сохраняется в памяти на месте самого старого. Для такого циркулирующего буфера может использоваться фиксированная область ОЗУ. При этом во время вычислений генерируются лишь последовательные значения адресов ОЗУ вне зависимости от того, какая операция запись или чтение выполняется в настоящий момент. Аппаратная реализация циклических буферов позволяет установить параметры буфера (адрес начала, длина) в программе вне тела цикла фильтрации, что позволяет сократить время выполнения циклического участка программы.

- 4. Сокращение длительности командного такта. Это во многом обеспечивается приемами, характерными для RISC-процессоров. Главными из них являются

размещение операндов большинства команд в регистрах, а также конвейеризация на уровне команд и микрокоманд. Конвейер имеет от 2 до 10 ступеней, что позволяет на различных стадиях выполнения одновременно обрабатывать до 10 команд. При этом используется генерация адресов регистров параллельно с выполнением арифметических операций, а также многопортовый доступ к памяти. Сюда же можно отнести и такой прием, характерный для универсальных микропроцессоров с **EPIC-архитектурой**, как применение команд со сверхбольшой длиной слова (VLIW), генерируемых на стадии компиляции программы. Этому же служит и рассмотренная выше **гарвардская архитектура** процессора, характерная для однокристальных микроконтроллеров.

- 5. Наличие на кристалле процессора внутренней памяти, что роднит ЦСП с однокристальными МК. Встроенная в процессор память обычно имеет значительно большее быстродействие, чем внешняя. Наличие встроенной памяти позволяет значительно упростить систему в целом, уменьшить ее размеры, энергопотребление и стоимость. Емкость внутренней памяти является результатом определенного компромисса. Ее увеличение ведет к удорожанию процессора и увеличивает энергопотребление, а ограниченная емкость памяти программ не позволяет хранить сложные алгоритмы. Большинство DS P-процессоров с фиксированной точкой имеют малую емкость внутренней памяти, обычно от 4 до 256 Кбайт, и невысокую разрядность внешних шин данных, связывающих процессор с внешней памятью. В то же время ЦСП с плавающей точкой обычно предполагают работу с большими массивами данных и сложными алгоритмами и имеют либо встроенную память большой емкости, либо большую разрядность адресных шин для подключения внешней памяти (а иногда и то, и другое).

- 6. Широкие возможности по аппаратному взаимодействию с внешними устройствами, включающие:

- большое разнообразие интерфейсов, в том числе контроллеры локальной промышленной сети CAN, встроенные коммуникационные (SCI) и периферийные (SPI) интерфейсы, I2C, UART;

- несколько входов для аналоговых сигналов и, соответственно, встроенный АЦП;

- выходные каналы широтно-импульсной модуляции (ШИМ);

- развитую систему внешних прерываний;

- контроллеры прямого доступа в память.

- 7. В некоторых DSP-семействах предусмотрены специальные аппаратные средства, облегчающие создание мультипроцессорных систем с параллельной обработкой данных для наращивания производительности.

- 8. DSP-процессоры широко используются в мобильных устройствах, где потребляемая мощность является основной характеристикой. Для снижения энергопотребления в сигнальных процессорах применяется множество методов, в том числе уменьшение напряжения питания и введение функций управления потреблением, например, динамическое изменение тактовой частоты, переключение в спящий или дежурный режим либо отключение не используемой в данный момент периферии. Следует отметить, что эти меры оказывают значительное воздействие на

скорость работы процессора и при некорректном использовании могут привести к неработоспособности проектируемого устройства (в качестве примера можно упомянуть некоторые сотовые телефоны, которые в результате ошибок в программах управления энергопотреблением иногда переставали включаться) или к ухудшению его эксплуатационных характеристик (например, значительному времени восстановления работоспособности при выходе из спящего режима).

#### Система команд сигнальных процессоров

Система команд сигнальных процессоров имеет многие черты систем команд универсальных микропроцессоров (особенно с RISC-архитектурой) и однокристальных микроконтроллеров. Она включает в себя основные арифметические и логические операции и команды переходов, но в меньшем, чем в универсальных МП, количестве. Число режимов адресации операндов также относительно невелико. Команда имеет простой, четко заданный формат. Длина команды составляет одно, реже два 16-разрядных слова. Однако наряду с использованием сокращенного набора команд, в DSP-процессорах применяются и такие характерные для ММХ-обработки аппаратно поддерживаемые инструкции, как команды поиска минимума и максимума, получения абсолютного значения, сложения с насыщением, при котором в случае переполнения при сложении двух чисел результату присваивается максимально возможное в данной разрядной сетке значение. Это ведет к уменьшению количества конфликтов в конвейере и повышает эффективность работы процессора.

С другой стороны, ЦСП содержат ряд команд, наличие которых обусловлено спецификой их применения и которые вследствие этого редко присутствуют в микропроцессорах других типов. Прежде всего это, конечно, команда умножения с накоплением суммы МАС, лежащая в основе ЦОС: А = В\*С+А. В системах команд некоторых сигнальных процессоров можно при программировании указать число выполнений этой команды в цикле и правила изменения индексов для адресации операндов В и С. При этом в отличие от команд повторения обычных процессоров сигнальный процессор может аппаратно поддерживать проверку условия завершения цикла. Сюда же можно отнести и команды сдвига (перезаписи) в соседнюю ячейку ОЗУ данных, поддерживающие работу циклического буфера для подготовки умножения в следующем такте.

Для эффективной реализации алгоритмов БП $\Phi$  в систему команд некоторых DSP-процессоров включены возможности адресации с реверсированием бит адреса.

Программирование микропроцессоров этого класса также имеет свои особенности. Значительное удобство для разработчика, обычно связываемое с использованием языков высокого уровня, в большинстве случаев оборачивается получением менее компактного и быстрого кода. Так как особенности ЦОС предполагают работу в реальном времени, это приводит к необходимости использования для решения тех же задач более мощных и дорогих DSP. Такая ситуация особенно критична для крупносерийной продукции, где разница в стоимости более производительного DSP или дополнительного процессора играет важную роль. В то же время в современных условиях скорость разработки (и, следовательно, выхода

нового изделия на рынок) может принести больше выгод, чем затраты времени на оптимизацию кода при написании программы на ассемблере.

Компромиссным подходом здесь служит использование ассемблера для написания наиболее критичных с точки зрения время- и ресурсоемкости участков программы, в то время как основная часть программы пишется на языке высокого уровня, как правило, Си или Си++.

Спектр компаний, представленных на рынке DSP-процессоров, более широк, чем среди производителей универсальных микропроцессоров.

В настоящее время доминирующее положение на рынке ЦСП занимает фирма Texas Instruments. Среди остальных производителей этой продукции следует выделить фирмы Freescale Semiconductor (ранее подразделение Motorola), Analog Devices, Phillips Semiconductors и Agere Systems (Lucent MicroelecTRonic). Следует отметить, что данный рынок является очень подвижным, что приводит к его постоянному перераспределению между компаниями и появлению на рынке новых игроков.

Таблица 1: Основные производители сигнальных процессоров (2006 г.)

| Компания                | Доля рынка |

|-------------------------|------------|

| Texas Instruments       | 54,3 %     |

| Freescale Semiconductor | 14,1 %     |

| Analog Devices          | 8,0%       |

| Philips Semiconductors  | 7,5%       |

| Agere Systems           | 7,3%       |

| Прочие                  | 8,8%       |

С ростом числа областей применения ЦОС и сложности алгоритмов обработки возрастают требования к сигнальным процессорам в плане повышения быстродействия и оснащенности интерфейсными и другими специализированными узлами. В настоящее время на рынке присутствует множество типов ЦСП, как универсальных, так и ориентированных на достаточно узкий круг задач. Естественно, ни один из процессоров не может быть оптимальным для всех приложений. Поэтому первая задача разработчика - выбор процессора, наиболее подходящего по производительности, цене, наличию определенной периферии, потребляемой мощности, простоте использования и другим критериям.

Например, для таких портативных устройств, как мобильные телефоны, портативные цифровые плееры, первостепенными являются стоимость, степень интеграции и потребляемая мощность, а максимальная производительность зачастую не нужна, так как обычно влечет за собой значительное повышение потребляемой мощности, не давая преимуществ при обработке относительно низкоскоростных аудиоданных. В то же время для гидроакустических или радиолокационных систем

определяющими параметрами являются скорость работы, наличие высокоскоростных интерфейсов, а стоимость является второстепенным критерием.

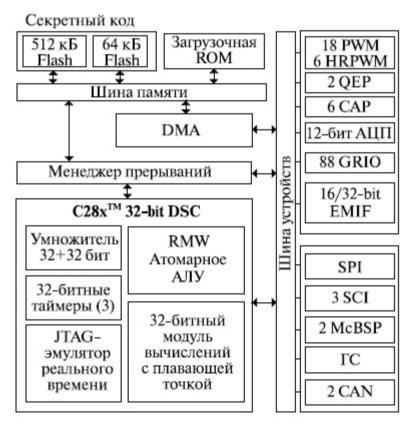

Рассмотрим структуру и основные характеристики DSP-процессора на примере процессора цифровой обработки сигналов TMS320F2833x фирмы Texas Instruments.

Семейство этих процессоров представляет собой 32-разрядные цифровые сигнальные процессоры, объединяющие в себе мощные и эффективные технологии цифровой обработки сигналов с богатым набором периферийных устройств и простотой использования. Данная платформа процессоров изначально создавалась для приложений управления электродвигателями и электроприводами. В процессе развития они приобрели более развитую периферию и мощное 32-разрядное ядро сигнального процессора, за счет чего область их применения значительно расширилась и в настоящее время включает в себя также те области, где ранее традиционно применялись мощные микроконтроллеры. В настоящее время семейство включает в себя модели TMS320F2832, TMS320F2833 и TMS320F2835, отличающиеся частотой синхронизации, емкостью внутренней памяти и некоторыми другими количественными параметрами. В дальнейшем описании мы будем опираться на характеристики ЦСП модели TMS320F2835, структура которого представлена на рисунке

Таблица 2: Цифровой сигнальный процессор TMS320F2835

Процессор содержит блок обработки чисел с плавающей точкой, аппаратный умножитель, позволяющий выполнять за один цикл операцию типа 32х32 бит МАС либо две операции типа 16х16 бит МАС, а также так называемое атомарное АЛУ, которое обеспечивает выполнение за 1 цикл таких операций, как чтение-модификация-запись по любому из адресов памяти, что позволяет значительно повысить производительность и эффективность кода.

В состав процессора входят разнообразные запоминающие устройства:

- однопортовое ОЗУ (SARAM) объемом 34К\*16 слов; оно состоит из 8 блоков с организацией 4К 16-разрядных слов каждый и 2 блоков емкостью по 1К\*16 байт, в которых может храниться таблица векторов прерываний;

- ПЗУ (в этом процессоре обозначается как OTP one-time programmable): 1K\*16 разрядов;

- модуль Flash-памяти емкостью 512 Кбайт, который позволяет разработчику многократно изменять программу в процессоре, в том числе и непосредственно в готовом изделии, что обеспечивает максимальную легкость и удобство обновления программных версий приборов. Flash-память разбита на секторы, что позволяет пользователю программировать лишь часть памяти, не осуществляя предварительного полного стирания. Однако следует отметить, что Flash-память работает медленнее, чем ядро процессора и его основная память (память программ и память данных), поэтому некоторые части кода, такие как функции прерываний, а также функции, критичные к скорости выполнения, не могут выполняться из Flash;

- загрузочная память Boot ROM объемом 8K слов по 16 разрядов.

Записанная здесь микропрограмма выполняется ядром процессора каждый раз при подаче питания на процессор, а также после сброса. Результатом ее выполнения является передача функций загрузки программы, которую ЦСП должен выполнить, определенному периферийному устройству, подключенному по интерфейсу SPI, I2C и т. п., либо внутренней или внешней Flash-памяти. Здесь же содержатся таблицы нормализованных значений математических функций, таких как синус, косинус, а также таблицы векторов прерываний.

Flash-память, ПЗУ и блоки L0-L7 ОЗУ защищены 128-разрядным секретным ключом.

Память имеет возможность расширения до 2M\*16 слов посредством 16/32-разрядной шины EMIF.

Все процессоры семейства F2833х являются высокоинтегрированными устройствами и содержат:

- последовательные интерфейсы, включающие:

- 2 сетевых порта CAN, позволяющие организовать две независимо работающие CAN-сети для подключения внутренних интеллектуальных устройств и внешних, например, для связи с системами управления верхнего уровня;

- 3 порта асинхронного последовательного интерфейса SCI (UART), используемых для межпроцессорной или другой асинхронной связи в дуплексном и полудуплексном режимах;

- порт синхронного последовательного интерфейса (SPI);

- шину I2C;

- 2 буферированных последовательных порта McBSP;

- 88 последовательных портов ввода-вывода общего назначения (GPIO) с независимым тактированием и возможностью многоканальных режимов работы с поддержкой блочной передачи по каждому каналу;

- порт JTAG, позволяющий отлаживать систему в реальном времени;

- 12 -разрядный 16-канальный АЦП со временем преобразования сигнала 80 нс, что на сегодняшний день является лучшим результатом среди АЦП, встроенных в ЦСП;

- 6 контроллеров **прямого доступа в память**. Передача данных по каналу ПДП выполняется пакетами. Длина каждого пакета не более 32 16-разрядных слов. Общее число пакетов в передаче до 65535. По завершении передачи канал ПДП может генерировать запрос прерывания для новой инициализации контроллера ПДП.

- три 32-разрядных таймера;

- сторожевой таймер, предохраняющий систему от зависания;

- шесть 32-разрядных каналов захвата внешних событий ( enhanced capture eCAP ), используемых в системах, где важно точное согласование во времени внешних событий, например, при измерении периода следования сигналов;

- два 32-разрядных модуля eQEP ( enhanced quadrature encoder pulse ), предназначенных для поддержки измерений скорости и частоты, детектирования заклинивания ротора и определения его положения, контроля неисправностей. Могут использоваться как дополнительные модули CAP;

- расширенный блок широтно-импульсной модуляции ( enhanced pulse-width modulator EPWM ), обеспечивающий функционирование 18 каналов ШИМ, 6 из которых работают на повышенной частоте с разрешением 150 пс. Широкие возможности этого блока связаны с основными областями применения данного сигнального процессора: автомобильная промышленность, промышленная автоматика, измерительные приборы, преобразователи мощности.

# Цифровой сигнальный процессор ADSP BF561

В ряде задач, например, в задачах обработки видеоизображений с высоким разрешением, мощности одного, даже высокопроизводительного процессора оказывается недостаточно. Решение этой проблемы идет по двум направлениям.

Во-первых, это создание **мультипроцессорных систем**. В некоторых DSP-семействах для наращивания производительности предусмотрены специальные аппаратные средства, облегчающие создание мультипроцессорных систем с параллельной обработкой данных.

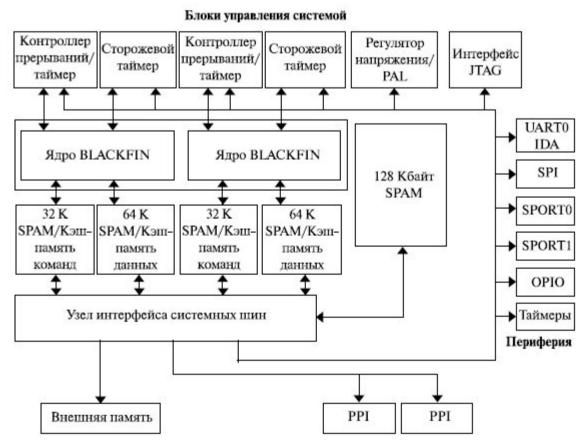

Во-вторых, это **разработка многоядерных цифровых сигнальных процессоров**, аналогично такому же направлению в развитии архитектуры универсальных МП. Рассмотрим второй подход на примере цифрового сигнального процессора ADSP BF561 фирмы Analog Devices.

Основу процессора составляют два вычислительных ядра BLACKFIN, каждое из которых имеет свой набор ресурсов, включающий вычислительный блок, блок управления и набор регистров.

Основу вычислительного блока составляют два 16-разрядных МАСустройства. Так как процессор работает на частоте 600 МГц, это обеспечивает выполнение МАС-операций с эквивалентной частотой 2,4 ГГц (по 2 МАС-устройства в каждом из двух ядер).

Помимо этого в вычислительный блок каждого из ядер входят следующие устройства:

- два 40-разрядных АЛУ для выполнения обычных арифметических и логических операций над 16- и 32-разрядными данными;

- 40-разрядное устройство сдвига, выполняющее помимо собственно сдвигов различных типов также нормализацию и извлечение экспоненты, обработку отдельных бит или наборов бит;

- четыре 8-разрядных видео-АЛУ, которые поддерживают некоторые операции над 8-разрядными данными, характерные для задач обработки видеоизображений;

- блок регистров общего назначения, включающий восемь 32-разрядных регистров, каждый из которых в зависимости от конкретной операции может рассматриваться как одно 32-разрядное слово или как два 16-разрядных.

Рисунок 5: Структура процессора ADSP BF561

Каждое ядро процессора имеет собственную память емкостью 100 Кбайт, доступную только ему и работающую на частоте ядра: 32 Кбайт памяти команд, из которых 16 Кбайт могут быть сконфигурированы как кэш команд, 64 Кбайт памяти данных, из которых 32 Кбайт

могут быть сконфигурированы как кэш данных, и 4 Кбайта специального ОЗУ для сохранения контекста (scratchpad).

На кристалле также имеется менее быстродействующая (работающая на половине частоты ядра) память второго уровня объемом 128 Кбайт, доступная обоим ядрам. В ней могут храниться как команды, так и данные.

К процессору через 32-разрядную шину данных может быть подключено до четырех банков внешней памяти емкостью от 16 до 128 Мбайт каждый с общей емкостью до 512 Мбайт.

Отдельного адресного пространства ввода/вывода в процессоре нет, и адресация ко всем ресурсам проводится посредством единого 32-разрядного адреса.

Процессор имеет 10-уровневый конвейер команд.

Процессор ADSP BF561 имеет очень богатый набор интегрированных периферийных узлов, часть из которых входит в состав каждого из ядер, а другие являются общими ресурсами процессора. Сюда относятся:

- 14 32-разрядных таймеров, 12 из которых являются общими и могут также программироваться как ШИМ-генераторы, а еще два используются каждым из ядер;

- два сторожевых таймера (по одному в каждом из ядер);

- 4-канальный внутренний контроллер ПДП для ускорения обмена между блоками памяти внутри процессора;

- 32- и 16-разрядный контроллеры ПДП; каждый из этих контроллеров имеет по 12 каналов для пересылок между внутренней памятью процессора и периферией и по 4 канала для пересылок между внутренней и внешней памятью;

- контроллер прерываний системы, который преобразует все прерывания от периферийных узлов, контроллеров ПДП и внешние прерывания (всего 61 источник) в прерывания ядра общего назначения;

- по одному контроллеру прерываний в каждом из ядер, которые поддерживают 9 прерываний общего назначения и выделенные прерывания: сброса, эмуляции, немаскируемое прерывание, прерывания от таймеров и т. д.;

- два 16-разрядных параллельных порта PPI, которые позволяют без использования дополнительной логики подключать к процессору многие стандартные АЦП, ЦАП, видеокодеры и декодеры;

- 48 программируемых портов ввода-вывода общего назначения (GPIO);

- набор стандартных последовательных интерфейсов SPI, SPORT и UART (с поддержкой IrDA) и т. д.

Процессор поддерживает режимы прямой адресации, косвенной адресации с пред- и постинкрементом и специфические для задач цифровой обработки сигналов режимы циклической адресации и адресации с реверсированием бит адреса.

Система команд процессора, аналогично RISC-микропроцессорам, имеет структуру, ориентированную на регистры и поддержку языков высокого уровня.